# **Table of Contents**

| Preface    | I/O Timing<br>Execution Speed                                                                                                                                                                                                                                                 | 1<br>1                                                               |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|            | Cost<br>Debugging Tool                                                                                                                                                                                                                                                        |                                                                      |

| Chapter 1. | Introduction<br>Introduction<br>Highlights<br>Installing MPSIM<br>System Requirements<br>Document Conventions<br>Terminology<br>Breakpoints<br>Program Counter (PC)<br>Disassembler<br>Step<br>Symbols<br>Trace<br>View screen<br>Device-Specific Support<br>Customer Support | 3<br>3<br>4<br>4<br>4<br>4<br>4<br>5<br>5                            |

| Chapter 2. | The MPSIM Environment<br>Introduction<br>Highlights<br>User Interface<br>Invoking MPSIM<br>I/O Pins<br>I/O Pin Modeling<br>Pin Signals<br>CPU Model<br>Reset Conditions<br>Sleep<br>WDT<br>Registers<br>Hardware Stack                                                        | 7<br>7<br>9<br>9<br>.10<br>.10<br>.10<br>.11<br>.11<br>.11<br>.11    |

|            | Push<br>Pop<br>Files Used and Generated By MPSIM<br>Command Files<br>Initialization File<br>Journal File<br>Stimulus File<br>Files Generated by the Assembler<br>Listing File<br>Input Hex File<br>Output Hex File<br>Output Hex File<br>Trace File<br>HEX Code Formats       | 12<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>15<br>15<br>15 |

| Chapter 3. | Tutorial                                               | 17 |

|------------|--------------------------------------------------------|----|

|            | Introduction                                           |    |

|            | Highlights                                             | 17 |

|            | Assemble the Code                                      |    |

|            | Invoke the Simulator                                   | 18 |

|            | MPSIM.INI                                              | 19 |

|            | Load the Initialization File                           | 19 |

|            | Creating an initialization file                        | 19 |

|            | Load the Hex File                                      |    |

|            | Load the Stimulus File                                 |    |

|            | Set Up Trace Parameters                                |    |

|            | Set Up Breakpoints                                     |    |

|            | Execute the Hex Code                                   |    |

|            | Modify the Hex Code                                    |    |

|            | Exit the MPSIM Session                                 |    |

|            |                                                        |    |

| Chapter 4. | Functional Categories of MPSIM Commands                |    |

|            | Introduction                                           |    |

|            | Highlights                                             |    |

|            | Loading and Saving                                     |    |

|            | Inspecting And Modifying                               |    |

|            | Program Memory                                         |    |

|            | Registers                                              |    |

|            | Display Functions                                      |    |

|            | Patch Table                                            |    |

|            | Clearing Memory and Registers                          |    |

|            | Searching Memory                                       | 34 |

|            | Symbol Table                                           |    |

|            | Restore                                                | 35 |

|            | Execute and Trace                                      | 36 |

|            | Execution Instructions                                 | 36 |

|            | Tracing Execution                                      | 36 |

|            | Breakpoints                                            | 38 |

|            | View Screen                                            |    |

|            | Miscellaneous Commands                                 |    |

|            | MPSIM Commands                                         |    |

| Chapter 5. | MPSIM Commands                                         | 47 |

| onapter o. | Introduction                                           |    |

|            | Alphabetic Summary of MPSIM Commands                   |    |

|            | AB – Abort Session                                     |    |

|            | AD – Add Item to View Screen                           |    |

|            |                                                        |    |

|            | B – Set Breakpoint                                     |    |

|            | BC – Clear Breakpoint                                  |    |

|            | C – Continue Executing                                 |    |

|            | CK – Clock                                             |    |

|            | DB – Display All Active Breakpoints                    |    |

|            | DE – Delete Program Memory                             |    |

|            | DI – Display Program Memory in Symbolic Format         |    |

|            | DK – Define Key                                        |    |

|            | DL – Delete Symbol from Symbol Table                   |    |

|            | DM – Display Program Memory in Radix Designated Format |    |

|            | DP – Display All Patches                               |    |

|            | DR – Display All Registers                             |    |

|            | DS – Display Symbol Table                              | 65 |

|            |                                                        |    |

| DV – Delete View Screen Item<br>DW – Enable / Disable Watchdog Timer |    |

|----------------------------------------------------------------------|----|

| DX – Display Current Trace Parameters                                |    |

| E – Execute Program                                                  |    |

|                                                                      |    |

| EE – Modify EE Memory                                                |    |

| EL – Error Level                                                     |    |

| F - File Register Display/Modify                                     |    |

| FI – File Input                                                      |    |

| FM – Fill Memory                                                     | 71 |

| FW – Fuse Word                                                       | 72 |

| GE – Get Commands from an External File                              | 73 |

| GO – Reset and Execute                                               | 74 |

| GS – Generate Symbol                                                 |    |

| H – Help                                                             |    |

| IA – Insert/Inspect Assembly Code                                    |    |

| IN – Insert Instruction                                              |    |

|                                                                      |    |

| IP – Injection Point                                                 |    |

| IR – Initialize with Random Values                                   |    |

| LJ – Load and Execute Journal File                                   |    |

| LO – Load Object File                                                |    |

| LR – Load Registers                                                  |    |

| LS – Load Symbol File                                                | 81 |

| M – Display / Modify Program Memory at Address                       | 82 |

| NV – No View Screen                                                  |    |

| O – Output Modified Object Code                                      |    |

| P – Select Microcontroller                                           |    |

| Q – Quit                                                             |    |

| RA – Restore All                                                     |    |

| RE – Reset Elapsed Time and Step Count                               |    |

|                                                                      |    |

| RP – Restore Patches                                                 |    |

| RS – Reset Chip                                                      |    |

| SC – Display / Modify Processor Cycle Time                           |    |

| SE – Display / Modify I/O Pin                                        | 88 |

| SF – Search Program Memory for Register                              |    |

| SI – Search Program Memory in Symbolic Format                        | 90 |

| SM – Search Program Memory in Radix Designated Format                | 90 |

| SR – Set Radix                                                       | 91 |

| SS – Execute A Single Step                                           |    |

| ST – Read Stimulus File                                              |    |

| TA – Trace Address                                                   |    |

| TC – Trace Instructions                                              |    |

| TF – Trace to File/Printer                                           |    |

| TR – Trace Register                                                  |    |

| TY – Change View Screen                                              |    |

|                                                                      |    |

| UR – Upload Registers                                                |    |

| V – View Screen                                                      |    |

| Verbose – Echo to Screen                                             |    |

| W - Work Register Display / Modify                                   |    |

| WP – Watchdog Timer Period1                                          |    |

| ZM – Zero the Program Memory1                                        |    |

| ZP - Zero the Patch Table1                                           | 01 |

| ZR – Zero the Registers1                                             | 01 |

| ZT - Zero the Elapsed Time Counter1                                  |    |

|                                                                      | υz |

| Appendix A. | Troubleshooting Guide                             |     |

|-------------|---------------------------------------------------|-----|

|             | Introduction<br>Solutions to Some Common Problems |     |

|             |                                                   |     |

|             | Messages                                          |     |

|             | Informative Messages                              |     |

|             | Warning Messages<br>Error Messages                |     |

|             | Error messages                                    |     |

| Appendix B. | Sample File Listings                              |     |

|             | MPSIM.INI                                         | 117 |

|             | PIC16C5X.INC                                      | 117 |

|             | PIC16CXX.INC                                      | -   |

|             | PIC17CXX.INC                                      | 128 |

|             | SAMPLE.ASM                                        | 132 |

|             | SAMPLE.INI                                        |     |

|             | SAMPLE.STI                                        | 134 |

| Appendix C. | Customer Support                                  | 135 |

| Appendix 0. | Keeping Current with Microchip Systems            |     |

|             | Highlights                                        |     |

|             | Systems Information and Upgrade Hot Line          |     |

|             | Connecting to Microchip BBS                       |     |

|             | Using the Bulletin Board                          |     |

|             | Special Interest Groups                           |     |

|             | Files                                             |     |

|             | Mail                                              |     |

|             | Software Releases                                 |     |

|             | Alpha Release                                     |     |

|             | Intermediate Release                              |     |

|             | Beta Release                                      |     |

|             | Production Release                                |     |

| Appendix D. | Intel INTELLEC <sup>™</sup> Hexadecimal Format    | 141 |

|             | INHX8M                                            | 142 |

|             | 8-Bit Hex Format:                                 | 142 |

|             | 32-Bit Hex Format (.HEX)                          | 143 |

| Appendix E. | PIC16C5X User's Guide Addendum                    | 445 |

| Appendix E. | Introduction                                      |     |

|             | I/O Pins                                          |     |

|             | CPU Model                                         |     |

|             | Reset Conditions                                  | -   |

|             | Sleep                                             |     |

|             | WDT                                               |     |

|             | Stack                                             |     |

|             | Special Registers                                 |     |

|             | Peripherals                                       |     |

|             | Peripherals Supported                             |     |

|             |                                                   |     |

| Appendix F. | PIC16C64 User's Guide Addendum                    |     |

|             | Introduction                                      |     |

|             | I/O Pins                                          |     |

|             | Interrupts                                        |     |

|             | CPU Model                                         |     |

|             | Reset Conditions                                  |     |

|             | Sleep                                             | 150 |

|             |                                                   |     |

|             | WDT                            | 150 |

|-------------|--------------------------------|-----|

|             |                                |     |

|             | Stack                          |     |

|             | Special Registers              |     |

|             | Peripherals                    |     |

|             | Peripherals Supported          |     |

|             | Tcycle Limitation              |     |

|             |                                |     |

|             | TIMER1                         | -   |

|             | TIMER2                         | -   |

|             | CCP1                           |     |

|             | CAPTURE                        |     |

|             | COMPARE                        | 153 |

|             | PWM                            | 153 |

|             | SSP                            | 153 |

| Annondix C  | PIC16C65 User's Guide Addendum | 466 |

| Appendix G. |                                |     |

|             | Introduction                   |     |

|             | I/O Pins                       |     |

|             | Interrupts                     |     |

|             | CPU Model                      |     |

|             | Reset Conditions               |     |

|             | Sleep                          |     |

|             | WDT                            | 156 |

|             | Stack                          |     |

|             | Special Registers              |     |

|             | Peripherals                    |     |

|             | Peripherals Supported          |     |

|             | Tcycle Limitation              | 158 |

|             | TIMER0                         | 158 |

|             | TIMER1                         | 158 |

|             | TIMER2                         | 159 |

|             | CCP1 and CCP2                  | 159 |

|             | CAPTURE                        |     |

|             | COMPARE                        | 159 |

|             | PWM                            |     |

|             | SSP                            |     |

|             | USART                          |     |

|             |                                |     |

| Appendix H. | PIC16C71 User's Guide Addendum | 161 |

|             | Introduction                   | 161 |

|             | I/O Pins                       | -   |

|             | Interrupts                     |     |

|             | CPU Model                      |     |

|             | Reset Conditions               | 162 |

|             | Sleep                          | 162 |

|             | WDT                            | 162 |

|             | Stack                          | 162 |

|             | Special Registers              | 163 |

|             | Peripherals                    |     |

|             | Peripherals Supported          |     |

|             | Tcycle Limitation              |     |

|             | TIMER0                         |     |

|             | A/D Converter                  |     |

|             |                                |     |

| Appendix I. | PIC16C73 User's Guide Addendum | 165 |

|-------------|--------------------------------|-----|

|             | Introduction                   | 165 |

|             | I/O Pins                       | 165 |

|             | Interrupts                     | 165 |

|             | CPU Model                      |     |

|             | Reset Conditions               | 166 |

|             | Sleep                          | 166 |

|             | WDT                            |     |

|             | Stack                          | 166 |

|             | Special Registers              | 167 |

|             | Peripherals                    |     |

|             | Peripherals Supported          |     |

|             | Tcycle Limitation              |     |

|             | TIMER0                         | 168 |

|             | TIMER1                         | 168 |

|             | TIMER2                         | 169 |

|             | CCP1 and CCP2                  | 169 |

|             | CAPTURE                        | 169 |

|             | COMPARE                        | 169 |

|             | PWM                            | 169 |

|             | SSP                            | 169 |

|             | USART                          | 169 |

|             | A/D Converter                  | 169 |

| Appendix J. | PIC16C74 User's Guide Addendum | 171 |

| Appendix J. | Introduction                   |     |

|             | I/O Pins                       |     |

|             | Interrupts                     |     |

|             | CPU Model                      |     |

|             | Reset Conditions               |     |

|             | Sleep                          |     |

|             | WDT                            |     |

|             | Stack                          |     |

|             | Special Registers              |     |

|             | Peripherals                    |     |

|             | Peripherals Supported          |     |

|             | Tcycle Limitation              |     |

|             | TIMER0                         |     |

|             | TIMER1                         |     |

|             | TIMER2                         |     |

|             | CCP1 and CCP2                  | -   |

|             | CAPTURE                        |     |

|             | COMPARE                        |     |

|             | PWM                            |     |

|             | SSP                            | 175 |

|             | USART                          |     |

|             | A/D Converter                  |     |

|             |                                |     |

| Appendix K. | PIC16C84 User's Guide Addendum |     |

|             | Introduction                   |     |

|             | I/O Pins                       |     |

|             | Interrupts                     |     |

|             | CPU Model                      |     |

|             | Reset Conditions               |     |

|             | Sleep                          | 178 |

|             | WDT                        |     |

|-------------|----------------------------|-----|

|             | Stack                      |     |

|             | Special Registers          | 178 |

|             | Peripherals                | 179 |

|             | Peripherals Supported      | 179 |

|             | Tcycle Limitation          | 179 |

|             | TIMER0                     | 179 |

|             | EEPROM Data Memory         | 179 |

| Appendix L. | PIC17C42 Support           |     |

|             | Introduction               |     |

|             | I/O Pins                   |     |

|             | Special Function Registers |     |

|             | Interrupts                 |     |

|             | CPU Model                  |     |

|             | Reset Conditions           |     |

|             | Sleep                      |     |

|             | WDT                        |     |

|             | Stack                      |     |

|             | Instruction Set            |     |

|             | Special Registers          |     |

|             | Peripherals                |     |

|             | Tcycle Limitation          |     |

|             | TIMER0                     |     |

|             | TIMER1 and TIMER2          |     |

|             | TIMER3 and Capture         |     |

|             | PWM                        |     |

|             | USART                      |     |

|             | Memory Modes               |     |

| Appendix M. | PIC17C43 Support           |     |

|             | Introduction               |     |

|             | I/O Pins                   |     |

|             | Special Function Registers |     |

|             | Interrupts                 |     |

|             | CPU Model                  |     |

|             | Reset Conditions           |     |

|             | Sleep                      |     |

|             | WDT                        |     |

|             | Stack                      |     |

|             | Instruction Set            |     |

|             | Special Registers          |     |

|             | Peripherals                |     |

|             | Tcycle Limitation          |     |

|             |                            |     |

|             | TIMER0                     |     |

|             | TIMER3 and Capture         |     |

|             | PWM                        |     |

|             | USART                      |     |

|             | Memory Modes               |     |

|             | เพียากับเว้า เพียนธุร      |     |

| Appendix N.   | PIC17C44 Support           | 193 |

|---------------|----------------------------|-----|

|               | Introduction               |     |

|               | I/O Pins                   |     |

|               | Special Function Registers |     |

|               | Interrupts                 |     |

|               | CPU Model                  |     |

|               | Reset Conditions           |     |

|               | Sleep                      | 194 |

|               | WDT                        |     |

|               | Stack                      |     |

|               | Instruction Set            |     |

|               | Special Registers          | 195 |

|               | Peripherals                |     |

|               | . Tcycle Limitation        |     |

|               | TIMER0                     |     |

|               | TIMER1 and TIMER2          |     |

|               | TIMER3 and Capture         |     |

|               | PWM                        |     |

|               | USART                      |     |

|               | Memory Modes               |     |

| Worldwide Sal | les & Services             | 198 |

## Preface

MPSIM is a discrete-event simulator tool designed to:

- Imitate operation of Microchip Technology's PIC16C5X, PIC16CXX and PIC17CXX families of microcontrollers

- Assist users in debugging software that uses Microchip microcontroller devices

A discrete-event simulator, as opposed to an in-circuit emulator, is designed to aid in the debugging of the general logic of your software. The MPSIM discrete-event simulator allows users to modify object code and immediately re-execute, inject external stimuli to the simulated processor, and trace the execution of the object code. A simulator differs from an in-circuit emulator in three important areas: I/O timing, execution speed, and cost.

This manual covers MPSIM version 5.0 and later.

# I/O Timing

External timing in MPSIM is processed only once during each instruction cycle. Transient signals, such as a spike on MCLR smaller than an instruction cycle will not be simulated but may be caught by an in-circuit emulator. In MPSIM, external stimulus is injected just before the next instruction cycle execution.

## **Execution Speed**

The execution speed of a discrete-event simulator is several orders of magnitude less than a hardware-oriented solution. Users may view slower execution speed as a handicap or a blessing. Some discrete-event simulators are unacceptably slow. MPSIM however, attempts to provide the fastest possible simulation cycle.

## Cost

The cost of the debugging tool may be an issue with some developers. For this reason, Microchip Technology has developed this simulator to be a costeffective tool for debugging application software. MPSIM does not require any external hardware to the PC, which keeps the cost at a minimum.

## **Debugging Tool**

The simulator, however, is a great debugging tool. It is particularly suitable for optimizing algorithms. Unlike the emulator, the simulator makes many internal registers visible and can provide more complex break points.

If you are a new user, refer to Chapter 3 for a "Getting Started" tutorial.

Device specific information is provided in the appendices at the end of the manual.

## **Chapter 1. Introduction**

## Introduction

MPSIM is a discrete-event simulator designed to aid you in debugging your software applications for Microchip Technology's PIC16C5X, PIC16CXX, and PIC17CXX microcontrollers.

# Highlights

Whether you are an experienced user or a beginner, we strongly suggest that you read this chapter first since it provides information about:

- Installing MPSIM

- Documentation Conventions

- Terminology

- Device-Specific Support

- Customer Support

If this is your first time using MPSIM we also suggest that you go through the tutorial provided in Chapter 3. This tutorial introduces all files that are used or generated by the simulator and provides a good introduction to some of the most widely-used commands.

## **Installing MPSIM**

### **System Requirements**

MPSIM requires an IBM<sup>®</sup> PC/AT<sup>®</sup> or compatible running DOS version 5.0 or later. The PC needs a 3 1/2 inch floppy disk drive and at least 640K main memory. We recommend a hard disk with at least 5 MB of available space.

• On the PC, create a new directory for the MPSIM software and change to that directory:

### MKDIR SIM<RETURN>

#### CD SIM<RETURN>

Copy all the files on the MPSIM diskette into the above directory: COPY a:\\*.\*

After loading the software, MPSIM is ready to run.

## **Document Conventions**

This section describes the conventions this manual uses for the data you are to enter.

| Character             | Represents                                                                                                                            |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Square ([]) brackets  | Optional arguments                                                                                                                    |

| Curly ({ }) brackets  | Braces indicate group options. One or more options in the group is required.                                                          |

| Angle (< >) brackets  | Delimiters for special keys: <tab>, <esc>, etc.</esc></tab>                                                                           |

| Pipe ( ) characters   | Choice of mutually exclusive arguments; an OR selection                                                                               |

| Lower case characters | Type of data                                                                                                                          |

| Italic characters     | A variable argument; it can be either a type of<br>data (in lower case characters) or a specific<br>example (in uppercase characters) |

| Courier font          | User keyed data or output from the system                                                                                             |

### **TABLE 1.1- CHARACTER CONVENTIONS**

## Terminology

### **Breakpoints**

Source code locations where you want the code to cease execution.

### **Program Counter (PC)**

The address in the loaded program at which execution will begin or resume.

### Disassembler

Converts modified object code back into assembly-language code when a listing file wasn't loaded. Thus, mnemonic information can display even when you have made changes.

### Step

A single executable instruction. You can single-step through a program by executing one instruction at a time with the SS command. A stimulus file can inject values onto specified pins at specified steps.

### **Symbols**

Alphanumeric identifiers such as labels, constant names, bit location names and file register names. MPSIM understands both explicit data/addresses and symbols.

### Trace

A trace file can be created to illustrate the execution flow of your program. Each line in the trace file contains the object code, source line, step number, elapsed time, and file registers that have changed. Trace can be limited to a range of addresses, or to a specific file register address. Please see Chapter 3 "Tutorial" for examples on the trace file. When you trace the instructions, they always display on the screen. If you previously opened a trace file and have not closed it, MPSIM also appends the trace to the file.

### **View screen**

The portion of your monitor that dynamically displays the values in specified data areas. It is seven lines long. The V command creates a view screen; the AD command adds data areas to the display; the DV command deletes data area from the display; and the NV command deletes all data areas from the view screen.

## **Device-Specific Support**

MPSIM provides support for more than one family of microcontrollers. Chapters 1 - 5 contain general information about MPSIM, regardless of the target processor. Device-specific information can be found in the appendices at the end of this manual.

## **Customer Support**

If you have any questions about MPSIM, the first step is to check in Appendix A: Troubleshooting Guide, which contains a troubleshooting guide that provides some common error messages and their possible causes. Appendix C: Customer Support provides detailed information about how to connect to the Microchip Technology BBS. The BBS contains the most up-todate development systems software, application notes, as well as a variety of other useful information. If you still cannot find the answer, contact the sales office nearest you. Information and telephone numbers are presented on the last page of the manual.

# **Chapter 2. The MPSIM Environment**

## Introduction

Chapter 2 provides an introduction to the MPSIM debugging environment. It describes all data areas that can be simulated and presents general information about using the simulator. This chapter is highly recommended for first-time users.

# **Highlights**

The following topics will be covered:

- User Interface

- Invoking MPSIM

- I/O Pins

- CPU Model

- Hardware Stack

- Files Used and Generated By MPSIM

## **User Interface**

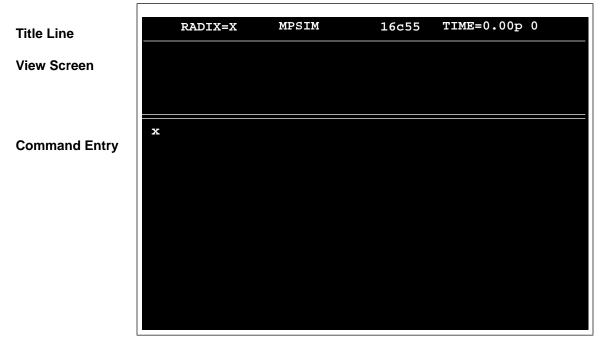

The user interface consists of three areas: the title line, the view screen and a command entry/display region. The title line remains in a fixed location at the top of the screen and lists the current hex file, the radix, the MPSIM version, the controller being simulated, cycle steps and elapsed time.

Figure 2.1 Start-up

The view screen displays user selected pin and register values. This area is created by the user typically through an initialization command file. This file will be in greater detail later in this chapter in "Files Used and Generated by MPSIM".

The command entry/display region occupies the remainder of the screen. Use this area to enter commands; MPSIM enters any responses to a command on the line or lines immediately following the command.

MPSIM can be invoked with any or a combination of the following options:

| Option | Description     | Default |

|--------|-----------------|---------|

| -V     | verbose         | off     |

| -m     | monochrome mode | off     |

| -a     | ASCII only      | off     |

## **Invoking MPSIM**

Invoke MPSIM by typing MPSIM at the DOS prompt, or by typing MPSIM\_DP for the PIC17C42 in the extended microcontroller or microprocessor mode. MPSIM is faster than MPSIM\_DP. MPSIM\_DP supports the larger memory modules.

To load a file into the simulator, use the following command:

#### %LO filename [FORMAT] <RETURN>

The '%' is MPSIM's prompt. Exit MPSIM by using the AB or Q command. Obtain help with the H command.

## I/O Pins

There is a list of viewable and modifiable pins for each microcontroller in its appendix. These pin names are loaded when a processor is selected and are the only ones that MPSIM recognizes as valid.

### I/O Pin Modeling

Because a conflict can occur when a pin is being driven internally (via an instruction) and externally (via stimulus file), the following table is provided to illustrate the possible conditions and the order in which MPSIM processes it.

| Is the pin being<br>driven<br>externally? | Is the pin<br>being<br>driven<br>internally<br>? | Resolution                                                                                      |

|-------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Yes                                       | Yes                                              | Chip wins.                                                                                      |

| No                                        | No                                               | The pins are essentially floating. The pins maintain the last external value they were driven.* |

| Yes                                       | No                                               | Simple.                                                                                         |

| No                                        | Yes                                              | Simple.                                                                                         |

|                                           |                                                  |                                                                                                 |

\* Note that this does not represent the actual behavior of the circuit when the I/O pin was last driven by the chip. However, typically, a used I/O pin (especially CMOS) would not be left floating.

### **Pin Signals**

At the end of each instruction all pins are checked for possible input or output.

- If the MCLR pin is cleared, MPSIM simulates a MCLR reset.

- The TRIS (or DDR for the PIC17CXX) status bits determine how MPSIM manipulates the port and file register bits. For example, the TRISA, RA0-RA5 and F5 registers work together; the TRISB, RB0-RB7 and F6 registers work together; and the TRISC, RC0-RC7 and F7 registers work together, etc.

- For TRIS status register bits that are set, MPSIM reads the corresponding port bit into the corresponding file register bit.

- For TRIS status register bits that are cleared, MPSIM writes the corresponding file register bit to the corresponding port bit (pin).

- Similarly, if any of the timer inputs are changed, the corresponding timer or its prescaler will increment.

- Any peripheral input (such as capture input) is acted upon.

- Any peripheral output (such as serial port output) is presented on the pin.

## **CPU Model**

### **Reset Conditions**

All reset conditions are supported by MPSIM.

A <u>Power-On-Reset</u>, for example, can be simulated by using the RS instruction. All special-purpose registers will be initialized to the values specified in the Microchip data sheet.

A  $\overline{\text{MCLR}}$  reset during normal operation or during SLEEP, for example, can easily be simulated by driving the  $\overline{\text{MCLR}}$  pin low (and then high) either via the stimulus file or by using the SE command.

A WDT time-out reset is simulated when WDT is enabled (see DW command) and proper prescaler is set (by initializing OPTION register appropriately for the PIC16CXX family or by using the FW command for the PIC17CXX family) and WDT actually overflows. WDT time-out period is approximately the "normal" time for the device being simulated (to closest instruction cycle multiple).

The Time-out ( $\overline{TO}$ ) and Power-down ( $\overline{PD}$ ) bits in the Status register reflect the reset condition. This feature is useful for simulating various power-up and time out forks in the user code.

### Sleep

MPSIM simulates the SLEEP instruction, and will appear "asleep" until a wake-up from sleep condition occurs. For example, if the Watchdog timer has been enabled, it will wake the processor up from sleep when it times out (depending upon the prescaler setting).

Another example of a wake-up-from-sleep condition, would be Timer1 wakeup from sleep. In this case, when the processor is asleep, Timer1 would continue to increment until it overflows, and if the interrupt is enabled, will wake the processor on overflow and branch to the interrupt vector.

Wake-up from SLEEP through interrupt is fully simulated in the PIC16CXX and PIC17CXX products.

### WDT

The Watchdog timer is fully simulated in the MPSIM simulator. Because it is fuse-selectable on the device, it must be enabled by a separate command (see the DW command) in MPSIM. The period of the WDT is determined by the prescaler settings. The basic period (with prescaler = 1) is approximated at 18 ms (for the PIC16C5X and PIC16CXX families and 12 ms for the PIC17CXX families).

### Registers

MPSIM simulates all registers. Certain special-function registers or nonmapped registers can be added to the viewscreen or modified like any other register. Examples are timer prescaler or postscalers.

All registers are initialized appropriately at various reset conditions.

Please see the appendix of the microcontroller in question for a list of additional registers.

| Register Name | Function                                     |

|---------------|----------------------------------------------|

| W             | Working Register                             |

| TRISA         | Tris register for Port A (PIC16C5X/PIC16CXX) |

| TRISB         | Tris register for Port B (PIC16C5X/PIC16CXX) |

| TRISX (etc)*  | (etc)*                                       |

| OPT           | Option register*                             |

\* Processor-dependent. For a complete list for a given processor, please refer to the device-specific appendix.

## Hardware Stack

### Push

The CALL instruction pushes the PC value + 1 to the top of the stack and loads the PC with the address of the subroutine being called. If the number of CALL instructions exceeds the depth of the stack, MPSIM will issue a "STACK OVERFLOW" warning message when executing or single-stepping through code. In the PIC16C5X family, the CALL instruction is the only instruction that causes an address to be pushed to the stack. The PIC16CXX and PIC17CXX families, however, support interrupts. When an interrupt occurs, the PC value + 1 is pushed to the stack and the PC is loaded with the address of the interrupt vector. The same error message will also be generated if too many addresses are pushed to the stack when MPSIM is executing or single-stepping through a program.

### Pop

RETLW instructions in the PIC16C5X and RETLW, RETURN and RETFIE instructions in the PIC16CXX and PIC17CXX instruction set remove or "pop" the last address pushed to the stack and loads its value into the PC. If an attempt is made to pop more values than the stack contains, MPSIM will issue a "STACK UNDERFLOW" warning message when executing or single-stepping through the program.

Because stack implementation is processor-family dependent, please refer to the appendix of the processor family in question for stack simulation.

## Files Used and Generated By MPSIM

MPSIM uses or creates the following I/O files.

- Command files

- Initialization files

- Journal files

- Stimulus files

- Assembler files

- HEX-Code formats

The following sections describe each of these files.

### **Command Files**

Command files are text files containing MPSIM commands. These MPSIM commands are executed with the GE command.

There are two special command files: MPSIM.INI and MPSIM.JRN. MPSIM.INI is the initialization file that MPSIM will automatically load on startup. MPSIM.JRN is a file containing all commands executed in the previous session.

### **Initialization File**

When MPSIM is invoked, it automatically performs the MPSIM commands in MPSIM.INI. Common commands in this file might create a standard view screen and/or initialize data areas. Figure 3.2 in Chapter 3 lists an example initialization file and Figure 3.3 in Chapter 3 shows the resulting view screen.

### **Journal File**

If you want to re-execute the most recent MPSIM session, LJ retrieves a list of the commands performed during the previous MPSIM session from MPSIM.JRN. This file is automatically created each time MPSIM is invoked. If you want to retain a journal file, copy it to another filename before reentering MPSIM. The first time you reenter MPSIM, the journal file is the same as you copied. However, when you exit via Q, the commands from the current MPSIM session will overwrite the previous journal file. Thereafter, you can access the copied file with GE.

As with all modern CAD/CAE tools, the concept of journal files is carried throughout MPSIM. That is, any command entered by the user is automatically stored in a journal file (named MPSIM.JRN). The journal file remains in the user's default directory regardless of the termination method (Quit or Abort). The LJ command loads and executes the journal file created during the previous simulator session. However, it doesn't store the commands from the previous journal file in the current journal file.

Performing the Q command removes the previous journal file, but using the AB (Abort) retains old journal file. The current MPSIM session commands are written over the previous journal file.

### **Stimulus File**

This file allows you to schedule bit manipulation by forcing MPSIM to drive given pins to given values at a specified input step. This scheduling is via a text file called a stimulus file. The stimulus file can force any pin to any value at any input step during program execution. The ST command reads the stimulus file into MPSIM. When you execute the loaded file with E, each time it looks for input, it reads the next step in the stimulus file. The first line of stimulus file always consists of column headings. It lists first the word "STEP," followed by the pins that are to be manipulated. The data below STEP represents the object file's input request occurrence. The data below each pin name is the input value. You may enter comments at the end of a line by preceding it with an exclamation mark (!). The following example illustrates the stimulus file format:

| STEP | pin 1 | pin 2 | ! These are pin names |

|------|-------|-------|-----------------------|

| 8    | 1     | 0     | ! followed by values  |

| 16   | 0     | 1     |                       |

| 24   | 1     | 0     |                       |

Other notes on the format of stimulus file:

- The steps in the stimulus file must be decimal, regardless of the radix in which you run your simulation

- The number of spaces separating data tokens is irrelevant

- Backslash (\) is a continuation mark at the end of a line and indicates that the following line continues the statement from the current line

| Step | RB2 | RA3 | RA2 | RA1 | RA0 | ! Column Headings          |

|------|-----|-----|-----|-----|-----|----------------------------|

| 3    | 0   | 0   | 1   | 0   | 0   | ! Stimulus before cycle 3  |

| 4    | 1   | 0   | 1   | 0   | 1   | ! Injected before cycle 10 |

| 9    | 1   | 1   | 0   | 1   | 0   | ! Injected before cycle 16 |

| 10   | 0   | 1   | 0   | 1   | 1   | ! Stimulus before cycle 3  |

| 15   | 0   | 0   | 0   | 0   | 0   | ! Injected before cycle 9  |

| 16   | 1   | 0   | 0   | 0   | 1   | ! Injected before cycle 15 |

Figure 2.2 Stimulus File

There are three other ways to inject stimulus to the I/O pins in addition to using the stimulus file. A "clock" can be assigned to an I/O pin, Alt-function keys can be assigned to the pins (only for use in "execute" mode), and they can be modified in "single step" mode. Details and syntax for each command can be found in Chapter 5. Please see CK, DK, and SE commands.

### Files Generated by the Assembler

The MPASM assembler generates by default all files necessary, for use with MPSIM. To assemble a file, invoke MPASM with the source file name as follows:

#### **MPASM** *filename*

The default assembler that MPSIM assumes is MPASM. To specify MPALC as the assembler, invoke MPSIM with the "-s" option.

### **Listing File**

The listing file contains the source code the assembler uses to create the object code being simulated. To display the source code throughout simulation, read in the listing file with the LO command. Otherwise, MPSIM uses the disassembler.

### **Input Hex File**

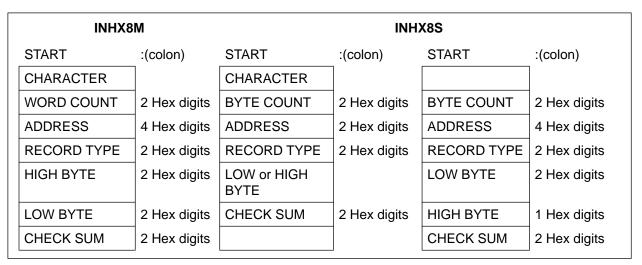

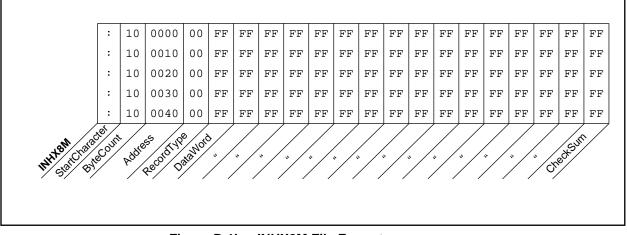

The input hex file contains the object code generated by the assembler. The LO command reads an hex file directly into program memory. The hex code format can be INHX8M or INHX8S. The default format is INHX8M.

### **Output Hex File**

At any time during simulation, the contents of the program memory can written to an external file with the O command. The hex code format can be INHX8S or INHX8M.

### Symbol File

The assembler generates the symbol file and contains a collection of symbols used in the source code. This file is used for symbolic debugging, and is automatically loaded when the LO command is used. The RA command clears the symbol file, and restores all original values.

### Trace File

If you open a trace file with the TF command and later trace execution, MPSIM writes the specified trace into the trace file as well as displaying the trace on-line.

### **HEX Code Formats**

The simulator is capable of reading or generating two different hex code formats as dictated by the LO and O commands: INHX8S or INHX8M. The default hex code format that the simulator recognizes is INHX8M, but any file format can be loaded by specifying the format when using the LO command. For example:

### LO Myfile INHX8S

will tell the simulator to load myfile.obh and myfile.obl. (The two files necessary for INHX8S format.) Similarly, modified hex code can be saved to disk in any format by using the following command:

### O Myfile INHX8M

The file that has been loaded into memory in any format will now be saved as a file in INHX8M format.

## Chapter 3. Tutorial

### Introduction

This chapter provides an introduction to MPSIM, the discrete-event simulator for Microchip Technology's PIC16C5X, PIC16CXX and PIC17CXX families of microcontrollers. It also presents a step-by-step tutorial through a sample program, SAMPLE.ASM. The tutorial is intended to familiarize you with the simulator and to provide an introduction to some of the most commonly used commands. The source code for SAMPLE.ASM and the other files used in the tutorial are available on your master disk, and can also be found in Appendix B at the end of the manual. If you do not have soft copies of the files for the tutorial, they can be created with any ASCII text editor. It is assumed that MPASM and MPSIM have been installed on your hard drive, and that all files used in the tutorial are in your working directory.

The program that is used in this tutorial, SAMPLE.ASM, is a software multiplier that takes two 8-bit numbers, "mulplr" and "mulcnd", and places the 16-bit result in "H\_byte" and "L\_byte" for the PIC16C54.

Because this chapter provides some background examples in addition to the tutorial, all steps that are part of the tutorial will have a step number in bold text to the left of the command in the margin.

# Highlights

This chapter covers the following information:

- Assemble the Code

- Involk the Simulator

- Load the Initialization File

- Load the Hex File

- Load the Stimulus File

- Set Up Trace Parameters

- Set Up Breakpoints

- Execute the Hex Code

- Modify the Hex Code

- Exit the MPSIM Session

## **Assemble the Code**

Before you can begin to use the simulator, you must first assemble SAMPLE.ASM. MPASM generates a hex file in INHX8M format by default. In addition to INHX8M, the following formats can be output:

### INHX8M

#### INHX8S

There is one default setting that the simulator assumes when it loads your code: the file format. The default file format for MPSIM is INHX8M, but any format that either assembler generates can be loaded into the simulator.

For this tutorial, we want the output file format to be INHX8M (the default format used by MPSIM), and the processor type to be PIC16C54. Type the following at the DOS prompt:

STEP 1:

MPASM sample /p16C54 <RETURN>

### Invoke the Simulator

STEP 2:

To invoke the simulator, simply type

MPSIM<RETURN> (if using the MPASM assembler)

or

#### MPSIM -s<RETURN> (if using the MPALC assembler)

at the DOS prompt.

The following screen will display:

| FZ: 100 | <b>F</b> 3: 00 | F4: 00 | F5: 00 | F6: 00 | F7: 00 |  |

|---------|----------------|--------|--------|--------|--------|--|

|         |                |        |        |        |        |  |

|         |                |        |        |        |        |  |

|         |                |        |        |        |        |  |

|         |                |        |        |        |        |  |

|         |                |        |        |        |        |  |

|         |                |        |        |        |        |  |

|         |                |        |        |        |        |  |

|         |                |        |        |        |        |  |

### **MPSIM.INI**

Observe the information in the command area and the information that is displayed in the view screen. The data areas appear in the view screen because an initialization file, MPSIM.INI is in your working directory. MPSIM.INI is simply an ASCII file that contains the same commands that appear in the command area. Every time MPSIM is invoked, it looks for a file called MPSIM.INI. If one exists on your working directory, all of the MPSIM commands appearing in that file will be executed, much like a DOS batch file. It is important to understand that an initialization file can be named anything. MPSIM.INI is unique in that it is automatically loaded when MPSIM is invoked.

## Load the Initialization File

Initialization files are very useful because they allow you to choose data areas that you wish to view, display them on the viewscreen, load your program, and create break points–all in one step. In other words, you can invoke MPSIM, load your initialization file, begin debugging, exit MPSIM, and return later, easily setting up the viewscreen the same way that you had it when you quit the program, simply by loading the initialization file.

### Creating an initialization file

One easy way to create an initialization file is to first invoke the simulator, type in commands that set up your viewscreen, set some break points, and then quit the simulator. When you quit, you will notice that a file "MPSIM.JRN" has been created. This "journal" file contains every command that you executed in the previous session. If the W register, or any other register was added to the viewscreen, the commands implementing this will be saved in the journal file. This file can then be edited using any text editor to remove commands such as "E" (execute) or "Q" (Quit), and then saved under another file name. It is necessary to remove commands such as "E" and "Q" because they will also be executed when you load your ANYTHING.INI file, and the simulator would set up your viewscreen, execute your code, and quit. It is also important to save the journal file under another name before invoking MPSIM a second time. Each time MPSIM is invoked, it overwrites the previous journal file, and if you did not rename the journal file, it will contain all commands executed in the current session.

For this example, we will use the initialization file called "SAMPLE.INI". We will load it by using the following command:

STEP 3:

### GE sample.ini <RETURN>

MPSIM executes the commands in the following SAMPLE.INI file.

| LO  | SAMPLE  |

|-----|---------|

| ST  | SAMPLE  |

| SR  | Х       |

| ZP  |         |

| ZR  |         |

| ZT  |         |

| RE  |         |

| P 5 | 54      |

| NV  |         |

| AD  | mulcnd  |

| AD  | mulplr  |

| AD  | H_byte  |

| AD  | L_byte  |

| AD  | count   |

| AD  | portb   |

| AD  | RB7,B,1 |

| AD  | RB6,B,1 |

| AD  | RB5,B,1 |

| AD  | RB4,B,1 |

| AD  | RB3,B,1 |

| AD  | RB2,B,1 |

| AD  | RB1,B,1 |

| AD  | RB0,B,1 |

Figure 3.2–Sample .INI Initialization File

This changes the viewscreen so that it displays the data areas that SAMPLE.HEX uses, in the most useful format.

| SAMPLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Reb IX+X  | MPS1 | 1 | 16c54              | TIM | E-0. | 0 966  |    |      |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|---|--------------------|-----|------|--------|----|------|---|

| aulend: 90 mul;<br>385:1 R85:1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |      |   | byte: 00<br>881: 1 |     | 00   | portb; | FF | R87: | 1 |

| AD mulpir<br>AD H_byte<br>AD L_byte<br>AD L_byte<br>AD count<br>AD portb<br>AD RB7.B,1<br>AD RB5.B,1<br>AD RB5.B,1<br>AD RB5.B,1<br>AD RB4.B,1<br>AD RB3.B,1<br>AD RB3.B | mory free |      |   | 2010               |     |      |        |    |      |   |

Figure 3.3– Sample.INI View Screen

The commands in this file create the viewscreen shown above and re-initialize data areas. The viewscreen now contains data areas that can be watched during the execution of SAMPLE.

### Load the Hex File

Notice that the LO command is listed in the SAMPLE.INI file. Because of this, the hex file was automatically loaded when SAMPLE.INI was loaded. If the LO command were not in the SAMPLE.INI file, you could load the file by typing in the following:

#### LO sample <RETURN>

It is important to realize that because we have assembled the code in the MPSIM default format (INHX8M), we do not have to specify the format being loaded. If we had assembled filename in any format other than INHX8M, we would have had to load the file in the following way:

#### LO filename format <RETURN>

MPSIM loads the named hex file, and then looks for a source file. If the file is available, it also loads the symbol table and the listing file.

## Load the Stimulus File

SAMPLE.INI has taken care of loading the stimulus file. You can see in the SAMPLE.INI file that the command:

#### ST sample.sti <RETURN>

was executed when the initialization file was loaded.

The stimulus file contains values that are to be input to the pins. When you execute the loaded program, at every instruction step specified in the stimulus file, MPSIM retrieves the input data, and injects their values to the pins.

| ! Stimulus file for SAMPLE.ASM |     |     |     |     |     |     |     |     |             |

|--------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------------|

| STEP                           | RB7 | RB6 | RB5 | RB4 | RB3 | RB2 | RB1 | rb0 | !PortB Pins |

| 3                              | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | ! 9 x 5     |

| 5                              | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |             |

| 65                             | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | ! 10 x 5    |

| 67                             | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |             |

| 127                            | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 1   | ! 27 x 3    |

| 129                            | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   |             |

| 191                            | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 1   | ! 17 x 7    |

| 193                            | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   |             |

| 253                            | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | ! 64 x 63   |

| 255                            | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 1   |             |

#### Figure 3.4 - SAMPLE.STI Stimulus File

The stimulus file for SAMPLE in figure 3.4 writes the multiplier and multiplicand values into simulated I/O port B. Since this port allows up to eight bits of data, the maximum value of the multiplier and multiplicand is 1111111 or 0xFF.

## **Set Up Trace Parameters**

A trace file is a file that contains executed instructions, timing information, and registers that have been modified. Using a trace file can be very helpful in determining where to inject stimulus and for creating a "hard copy" of the general execution flow of your program. There are five MPSIM commands dealing with traces:

- **TF** opens and closes a file for writing the traced data.

- TA traces all instructions between two specified addresses

- TC traces a specified number of instructions.

- TR traces instructions dealing with specified registers and values.

- DX displays the current trace parameters

Try some of the following exercises. All of the traces in these exercises will be printed to a file. If you would like to try printing your trace to a default printer, substitute "PRN" in place of the trace file name.

# Exercise 1: Trace the instructions between two labels, call\_m and main, and print the instructions to a file.

The first step is to create the trace file:

TF trace1.trc <RETURN>

Next, specify the range of the trace. Then, begin tracing the instructions. Hit any key to interrupt the trace.

TA main, call\_m <RETURN>

#### TC <RETURN>

# Exercise 2: Trace fourteen instructions (0x0E instructions) and write the trace to the file TRACE2.trc.

Restart the system by exiting MPSIM (q <RETURN>), and repeating steps 2 (Invoke the Simulator) and 3 (Load the Initialization File). Just as in Exercise 1, we will first open the trace file

#### TF trace2.trc <RETURN>

Then, we will trace the next fourteen instructions. Note that if the number of instructions to be traced is not specified, the trace will continue until a key is pressed.

#### TC E <RETURN>

**Note:** If you had specified the number of instructions to be executed as "14" instead of "E", twenty steps would have been executed since the radix is set to hexadecimal (the default radix in MPSIM).

| SAMPLE          | RADIX=X MPSIM                                                                                                   | 16c54 TIME=32.00µ 14                               |

|-----------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                 | lpir: FF H_byte: 80<br>884: 0 883: 0 882:                                                                       | L_byte:00 count:00 porth:05 807:0<br>1 881:0 880:1 |

| TF: Trace file  | is open (trace2.trc)                                                                                            |                                                    |

| < tc e          | The second se |                                                    |

|                 | goto start                                                                                                      | 14.00µ 1 1                                         |

| 300E 0040 start |                                                                                                                 | 16.00p Z 19:0 F3:1C                                |

| 100F 0002       | option                                                                                                          | 18.00F 3 :0PT:C8                                   |

| 3010 0206 main  | movf porth,w                                                                                                    | 110.00p 4 1W:FF F3:18                              |

| 3011 0030       | movel mulpir                                                                                                    |                                                    |

| 3012 0206       | movf porth,w                                                                                                    | 114.00P 6 1W:9 F3:18                               |

| 1013 0829       | movel mulcid                                                                                                    |                                                    |

| 1014 0900 call  |                                                                                                                 |                                                    |

| 3000 0072 mpg_S |                                                                                                                 | 122.00/ 9 IF12:0 F3:10                             |

| 1001 0073       | cirf L_byte                                                                                                     | (24.00p 10 (F13:0 F3:1C                            |

| 3002 0008       | movie 8                                                                                                         | 126.00p 11 10:8                                    |

| 3003 0034       | movaf count                                                                                                     | 128.00µ 12 (F14:8 F3:1C                            |

| 3004 8289       | movf mulcud, w                                                                                                  |                                                    |

| 1005 0403       | bof STATUS.CAR                                                                                                  | RY ; C (32.00) 14 (STATUS:10                       |

|                 |                                                                                                                 |                                                    |

Figure 3.5 –The trace information is printed to both the screen and the trace file.

#### Exercise 3: Check the current trace criteria.

#### DX <RETURN>

The current trace parameters display in the command entry area of the MPSIM screen.

## **Set Up Breakpoints**

Break points are used to artificially stop program execution so that you can review how the data has been manipulated or to see the contents of the Special Function Registers. There are three instructions that deal with breakpoints:

- DB displays all of the breakpoints currently set.

- **BC** clears one or all of the breakpoints currently set.

- **B** sets a break point.

- Exercise 1: Initialize the breakpoints by clearing any break points currently set. Enter the following command:

BC

Exercise 2: Set a breakpoint at MPY\_S. Enter the following command:

B mpy\_S<RETURN>

Exercise 3: Review all the breakpoints. Enter the following command:

DB<RETURN>

Exercise 4: Delete the breakpoint at MPY\_S. Enter the following command:

BC mpy\_S<RETURN>

## **Execute the Hex Code**

In addition to trace, there are three instructions that you can use to execute your code.

Е

SS

С

- E executes your code until it encounters a breakpoint or you press a key.

- **SS** single-steps through your instructions. That is, it executes one single instruction at the CPC.

- **C** Execute, ignoring "n" number of breakpoints.

- Exercise 1: Add a watch variable. Add the w register to the display.

### AD W <RETURN>

Exercise 2: Add two breakpoints and execute until the first breakpoint is encountered.

b main b mpy\_S

#### E <RETURN>

MPSIM executes until it encounters the first breakpoint or until a key is pressed. Watch the values change in the W, mulplr, H-Byte, and L-Byte registers.

#### Exercise 3: Execute instructions one step at a time.

#### SS <RETURN>

The SS instruction causes MPSIM to execute the instruction at the PC. Pressing <RETURN> at the MPSIM prompt re-executes the last command. Execute a second instruction by pressing <RETURN> again. Do this several times, watching how the values in the W, mulplr, H-Byte, registers change. This command can be used to single-step through your entire program to see the data values at each step, and to watch the flow of your program. If you supply an address with the SS command, MPSIM will modify the CPC to the address you specify and then will execute the instruction at that address. Remember that pressing <RETURN> will cause MPSIM to re-execute the same command, so that if you supplied an address with the command, the same address will be executed.

#### Exercise 4: Execute your program and break after the second breakpoint.

#### C 2 <RETURN>

MPSIM executes the instruction at the current CPC until the instruction immediately following the second break point. Watch the values change in the W, mulplr, H-Byte, and L-Byte registers.

## Modify the Hex Code

MPSIM has four types of commands which allow you to modify the hex code: search commands locate code that match specified criteria, display/modify commands automatically display specified code and allow you to change it, delete commands eliminate specified code, output commands allow the modified code to be saved to a file. For the following exercises, mulplr is stored in file register F10.

#### Exercise 1: Search for the next occurrence of F10, and change its contents to 0xFF.

#### SF 0, 1FF, F10 <RETURN>

You will see two code lines with the "mulplr" register label.

#### F F10 <RETURN>

After you type in the above command, you will see the current contents of register F10, followed by a colon. Type in the value 0xFF, and watch the contents of the file register change. You will see that the contents of "mulplr" will change since the value of "mulplr" is 0x10.